VHDL - Programming the Field Programmable Gate Array (FPGA)

Note: make sure you save the 2-to-4 component in the same directory with the 3-to-8 decoder in work.

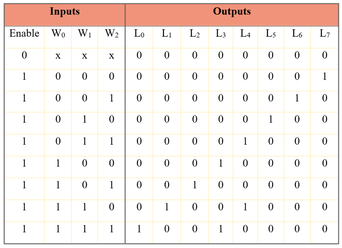

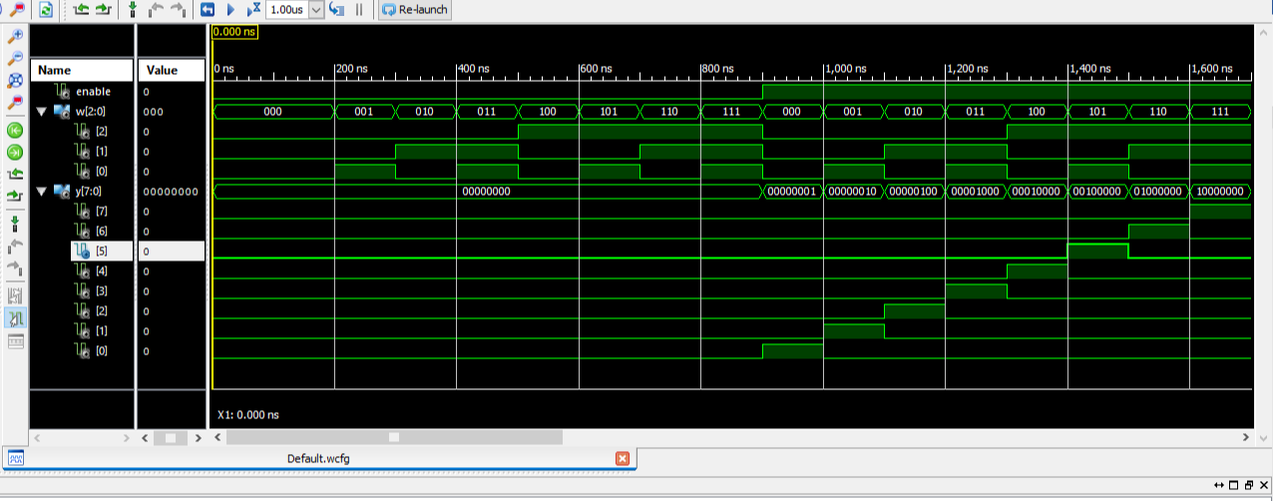

Then check the testbench code for syntax errors, and adjust the simulation run time to 100ns to allow the testbench code goes through all the possible combinations of the inputs. Next, run the simulation to obtain a waveform similar to the figure shown below.

3 to 8 Decoder Waveform

User Constraint File (UCF) for - Basys 2 FPGA Board

Create the implementation UCF file (.ucf) as shown bellow. This file contains the signal definitions and physical mapping of the pins on the Basys-2 FPGA board.

# PlanAhead Generated physical constraints NET "enable" LOC = N3; NET "w[0]" LOC = P11; NET "w[1]" LOC = L3; NET "w[2]" LOC = K3; NET "y[0]" LOC = M5; NET "y[1]" LOC = M11; NET "y[2]" LOC = P7; NET "y[3]" LOC = P6; NET "y[4]" LOC = N5; NET "y[5]" LOC = N4; NET "y[6]" LOC = P4; NET "y[7]" LOC = G1; Finally, generate a programming file (.bit), Connect the FPGA board to the computer and program the FPGA board using the ADEPT software.

For more information visit:

Basys 2 Reference Manual |

|